Hi everyone! I was trying to run this tunning tutorial https://tvm.apache.org/docs/v0.8.0/topic/vta/tutorials/autotvm/tune_relay_vta.html using TSIM and following the guide of “shin” in this post https://discuss.tvm.apache.org/t/auto-tuning-vta-solved-using-simulator-to-tune-resnet18-on-vta-successfully/13706/9 to make the tracker compatible for TSIM. My TVM version is 0.8.dev0, and I’m using ubuntu 18.04 and python 3.8 to tune this program.

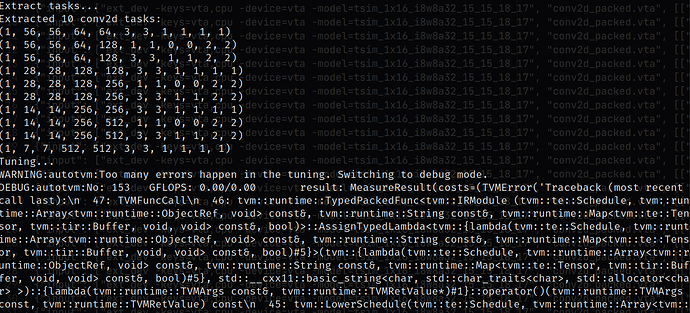

However, I met the Current/Best: 0.00/ 0.00 GFLOPS problem. Then it switched to the debug model and the error message in the following screen cut:

I found that these Error messages might be useful:

Check failed: (MatchCopyPattern(op->body, &ret)) is false: Cannot match copy pattern of for (i1, 0, 2) {\n for (i2, 0, 9) {\n for (i3, 0, 9) {\n for (i5, 0, 16) {\n if (tir.likely((((cthread*7) + i2) < 9))) {\n pad_data[((((i1*1296) + (i2*144)) + (i3*16)) + i5)] = tir.if_then_else(((((1 <= ((cthread*7) + i2)) && (((cthread*7) + i2) < 8)) && (1 <= i3)) && (i3 < 8)), placeholder[(((((((k_o.outer*1568) + (i1*784)) + (cthread*784)) + (i2*112)) + (i3*16)) + i5) - 128)], (int8)0)\n }\n }\n }\n }\n}\n'),), error_no=2, all_cost=0.023027896881103516, timestamp=1673096983.1819732) [('tile_b', [-1, 1]), ('tile_h', [-1, 7]), ('tile_w', [-1, 7]), ('tile_ci', [-1, 2]), ('tile_co', [-1, 4]), ('oc_nthread', 1), ('h_nthread', 2)],None,343

raise ValueError("Do not support pad on the innermost block")\nValueError: Do not support pad on the innermost block'),), error_no=2, all_cost=0.03188347816467285, timestamp=1673096983.1820433) [('tile_b', [-1, 1]), ('tile_h', [-1, 1]), ('tile_w', [-1, 1]), ('tile_ci', [-1, 2]), ('tile_co', [-1, 32]), ('oc_nthread', 1), ('h_nthread', 1)],None,124

Check failed: (MatchCopyPattern(op->body, &ret)) is false: Cannot match copy pattern of for (i1, 0, 2) {\n for (i2, 0, 3) {\n for (i3, 0, 3) {\n for (i5, 0, 16) {\n if (tir.likely(((((i2.outer.outer*2) + i2) + cthread) < 9))) {\n pad_data[((((i1*144) + (i2*48)) + (i3*16)) + i5)] = tir.if_then_else(((((1 <= (((i2.outer.outer*2) + i2) + cthread)) && ((((i2.outer.outer*2) + i2) + cthread) < 8)) && (1 <= (i3 + i3.outer))) && ((i3 + i3.outer) < 8)), placeholder[(((((((((k_o.outer*1568) + (i1*784)) + (i2.outer.outer*224)) + (i2*112)) + (cthread*112)) + (i3*16)) + (i3.outer*16)) + i5) - 128)], (int8)0)\n }\n }\n }\n }\n}\n'),), error_no=2, all_cost=0.025188922882080078, timestamp=1673096984.6041398)[('tile_b', [-1, 1]), ('tile_h', [-1, 1]), ('tile_w', [-1, 1]), ('tile_ci', [-1, 2]), ('tile_co', [-1, 16]), ('oc_nthread', 2), ('h_nthread', 2)],None,532

But I have no clue how to deal with it. Hope someone could give me some specific advice. Thanks for your help in advance!

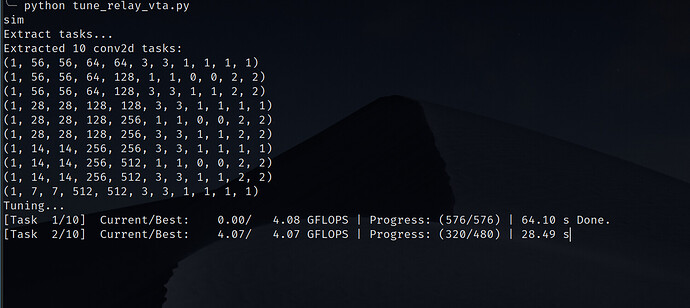

FYI, I can run FSIM normally as the screen shot as follows. But when it comes to TSIM, this problem will show.