Hi everyone,

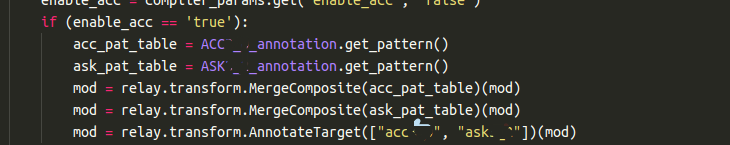

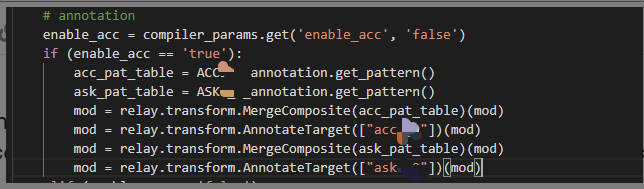

our team is trying to implement a BYOC flow with a default ARM cpu and two customized accelerators. We are trying to do the annotation and composite matching in the following:

The basic idea is to do: ACC pattern → ACC op → ASK pattern → ASK op, in which the order I think it makes sense: we want ACC to get more priority than ASK to implement the workload.

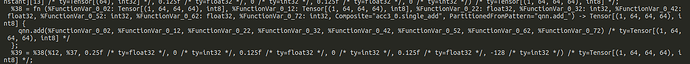

However, it shows the following compilation error:

![]()

Can BYOC experts help us resolve this issue? Seldom examples were presented for BYOC with more than one target, but I believe TVM support this case, am I correct??